Shahzaib Kashif

Micro Electronics Research Lab

About

I am a Research Assistant at MERL and a Software Engineering Graduate. I am majorly interested in designing hardware with the Software Engineering Methodologies using CHISEL HDL. I have been working on RISC-V ISA for the last 3+ years. I also have keen interest in Compilers, Edge Computing, and Tiny A.I/ML Models for Embedded/IoT Devices.

Interests

- RISC-V and CHISEL HDL

- Functional Programming

- Agile Hardware Design

- Compilers and IoT

- Edge Computing

Education

BSc in Software Engineering

Usman Institute of Technology (UIT), 2018 - 2022

Publications

(2023).

ChipShop: A Cloud-Based GUI for Accelerating SoC Design .

RISC-V Summit Europe.

(2023).

ChipShop: A Cloud-Based GUI for Accelerating SoC Design.

First FireSim and Chipyard User and Developer Workshop at ASPLOS 2023.

(2022).

SoC-Now: An Open-Source Web based RISC-V SoC Generator.

WOSET.

(2022).

Bitstream Chef.

WOSET.

Projects

*

Enhancing and Validating LiveHD’s Power Modeling Flow

Contributor in GSoC'23.

This project aims to improve and validate the power modeling flow of LiveHD, which is crucial for estimating power consumption in modern hardware designs. The current system needs improvements in stability, accuracy, compatibility, and performance. The project will tackle these issues by debugging the existing system, establishing a thorough validation methodology for power estimates, and optimizing the flow for larger netlists and VCD files.

This project aims to improve and validate the power modeling flow of LiveHD, which is crucial for estimating power consumption in modern hardware designs. The current system needs improvements in stability, accuracy, compatibility, and performance. The project will tackle these issues by debugging the existing system, establishing a thorough validation methodology for power estimates, and optimizing the flow for larger netlists and VCD files.

ChipShop

ChipShop is a cloud-based graphical user interface (GUI) that democratizes system-on-chip (SoC) design by simplifying the configuration and acceleration process on the open-source Chipyard platform. This user-friendly platform enables users to easily configure core types, caches, memory controllers, and other SoC features while supporting FPGA emulation, mapping, and the addition of new intellectual properties (IPs). ChipShop of ers automatic blackbox generation and integration for user-provided RTLs, streamlining the design process and reducing errors. The platform also includes real-time collaboration and version control features, making it ideal for large teams working on complex designs.

Implement Tilelink Uncached Heavyweight (TL-UH) in Caravan Framework

MENTORED in LFX Mentorship Spring'23 by RISC-V.

This Project aims at implementing the Tilelink Uncached Heavyweight (TL-UH) which is a standarized bus protocol by SiFive, in the Caravan Framwork. This way Caravan now supports a new bus (TL-UH) along with Wishbone and TL-UL that can be connected to any design by plug and play approach using the Generic Interfaces Architecture.

This Project aims at implementing the Tilelink Uncached Heavyweight (TL-UH) which is a standarized bus protocol by SiFive, in the Caravan Framwork. This way Caravan now supports a new bus (TL-UH) along with Wishbone and TL-UL that can be connected to any design by plug and play approach using the Generic Interfaces Architecture.

Adding Single Precision Floating Point (F) extension in NucleusRV Core

MENTORED in LFX Mentorship Spring'23 by RISC-V.

This Project aims to add the support of Single Precision Floating Point (F) extension of RISC-V in NucleusRV Core. This way the SoC-Now Generator’s scope will also expand so that now the parameter to include the F extension in the Core will become available. Henceforth increasing the value of the Generator and the Core standalone itself.

This Project aims to add the support of Single Precision Floating Point (F) extension of RISC-V in NucleusRV Core. This way the SoC-Now Generator’s scope will also expand so that now the parameter to include the F extension in the Core will become available. Henceforth increasing the value of the Generator and the Core standalone itself.

Bitstream Chef

An EDA Tool for rapid Bitstream Generation of Hardware Designs using a Graphical User Interface (GUI). Users can define the contraints for FPGA Prototyping in a simpler graphical manner. It is backed by Open Source Foss for FPGA (F4PGA) Toolcahin. Currently, a desktop application but targeted to be a cloud based web app.

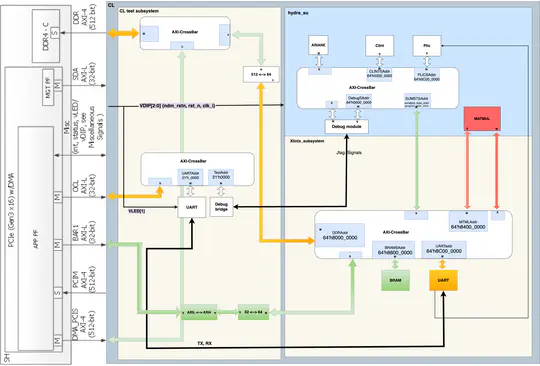

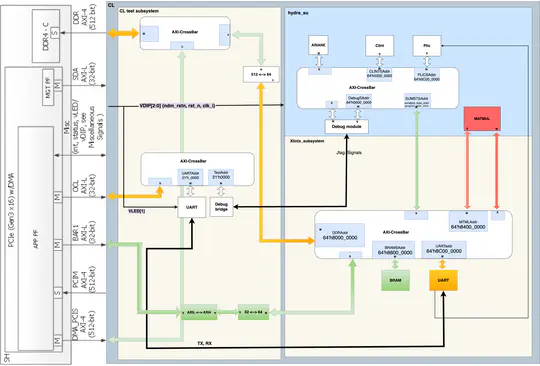

SoC-Now

Final Year Project (FYP).

SoC-Now is a SoC Generator that will generate customized/configurable SoCs rapidly. The generated SoC will be tested and verified based on industry standards. Additionally, SoC-Now will also provide the functionality of generating just only the Core standalone. Also, any Device or any other SoC Component can also be generated separately.

SoC-Now is a SoC Generator that will generate customized/configurable SoCs rapidly. The generated SoC will be tested and verified based on industry standards. Additionally, SoC-Now will also provide the functionality of generating just only the Core standalone. Also, any Device or any other SoC Component can also be generated separately.

Porting AOSP 12 Emulator to RISC-V RV64G

MENTEE in LFX Mentorship Spring'22 by RISC-V.

To Port the Android Open Source Project (AOSP) 12 Emulator to RISC-V RV64G system. This Project was in collaboration of The Linux Foundation (LFX), RISC-V International and PLCT Lab.

To Port the Android Open Source Project (AOSP) 12 Emulator to RISC-V RV64G system. This Project was in collaboration of The Linux Foundation (LFX), RISC-V International and PLCT Lab.

Linux Device Driver Development

The NOVA Project.

Developed multiple Linux Device Drivers and Configured the Zephyr RTOS in accordance with the system configuration. The entire system development was done on AWS-FPGA Platform. Separate AWS-FPGA Runtime Compatible Drivers were written to test the system during FPGA Emulation on Cloud.

Developed multiple Linux Device Drivers and Configured the Zephyr RTOS in accordance with the system configuration. The entire system development was done on AWS-FPGA Platform. Separate AWS-FPGA Runtime Compatible Drivers were written to test the system during FPGA Emulation on Cloud.

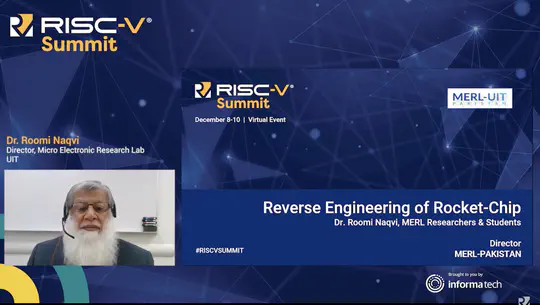

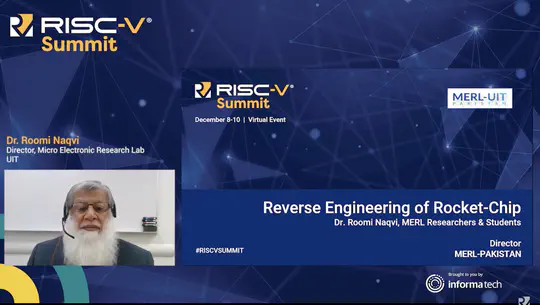

Reverse Engineering of Rocket-Chip

RISC-V Summit 2020.

Reverse Engineered the Rocket-Chip Generator by means of Software Engineering Approaches i.e to create Flowcharts, Class Diagram and Connect everything out in form of Block level diagrams. As a final result, a document called “Micro Architecture and Software Specification (MASS)” was created for the Rocket-Chip Generator for Core level specs only.

Reverse Engineered the Rocket-Chip Generator by means of Software Engineering Approaches i.e to create Flowcharts, Class Diagram and Connect everything out in form of Block level diagrams. As a final result, a document called “Micro Architecture and Software Specification (MASS)” was created for the Rocket-Chip Generator for Core level specs only.

Experience

Research Assistant

RISC-V CPU Logic Implementor (CHISEL)

Research Intern